UC1842/3/4/5 UC2842/3/4/5 UC3842/3/4/5

# Current Mode PWM Controller

## **FEATURES**

- Optimized For Off-line And DC To DC Converters

- Low Start Up Current (<1mA)</li>

- Automatic Feed Forward Compensation

- Pulse-by-pulse Current Limiting

- Enhanced Load Response Characteristics

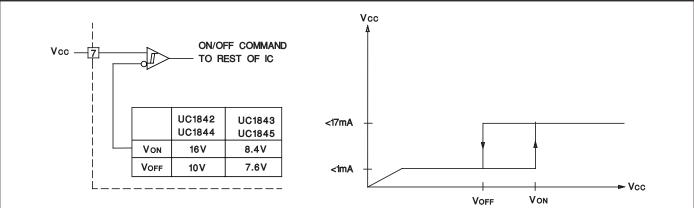

- Under-voltage Lockout With Hysteresis

- Double Pulse Suppression

- High Current Totem Pole Output

- Internally Trimmed Bandgap Reference

- 500khz Operation

- Low Ro Error Amp

## **DESCRIPTION**

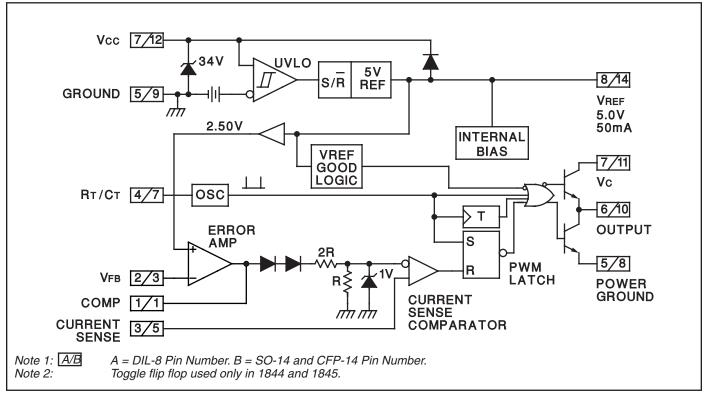

The UC1842/3/4/5 family of control ICs provides the necessary features to implement off-line or DC to DC fixed frequency current mode control schemes with a minimal external parts count. Internally implemented circuits include under-voltage lockout featuring start up current less than 1mA, a precision reference trimmed for accuracy at the error amp input, logic to insure latched operation, a PWM comparator which also provides current limit control, and a totem pole output stage designed to source or sink high peak current. The output stage, suitable for driving N Channel MOSFETs, is low in the off state.

Differences between members of this family are the under-voltage lockout thresholds and maximum duty cycle ranges. The UC1842 and UC1844 have UVLO thresholds of 16V (on) and 10V (off), ideally suited to off-line applications. The corresponding thresholds for the UC1843 and UC1845 are 8.4V and 7.6V. The UC1842 and UC1843 can operate to duty cycles approaching 100%. A range of zero to 50% is obtained by the UC1844 and UC1845 by the addition of an internal toggle flip flop which blanks the output off every other clock cycle.

#### **BLOCK DIAGRAM**

# **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| Supply Vo  | Itage (Low Impedance Source).              | 30V            |

|------------|--------------------------------------------|----------------|

| Supply Vo  | ltage (Icc < 30mA)                         | Self Limiting  |

| Output Cu  | rrent                                      | ±1A            |

| Output En  | ergy (Capacitive Load)                     | 5μJ            |

| Analog Inp | outs (Pins 2, 3)                           | 0.3V to +6.3V  |

| Error Amp  | Output Sink Current                        | 10mA           |

| Power Dis  | sipation at $TA \le 25^{\circ}X$ (DIL-8)   | 1Ω             |

| Power Dis  | sipation at $TA \le 25^{\circ}C$ (SOIC-14) | 725mW          |

| Storage To | emperature Range                           | 65°C to +150°C |

| Lead Tem   | perature (Soldering, 10 Seconds            | s) 300°C       |

| Note 1:    |                                            |                |

|            | All accompands and manifely a last at      |                |

All currents are positive into the specified terminal. Consult Packaging Section of Databook for thermal limitations and considerations of packages.

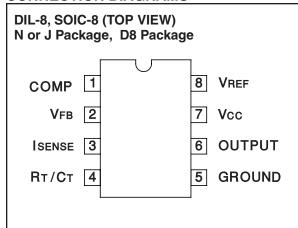

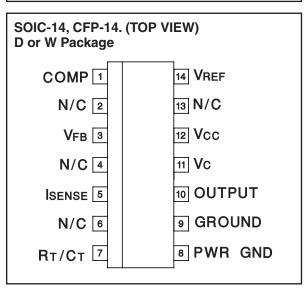

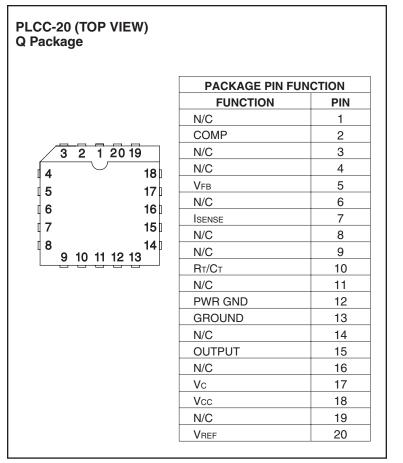

# **CONNECTION DIAGRAMS**

# **DISSIPATION RATING TABLE**

| Package | TA ≤ 25°C    | Derating Factor | TA ≤ 70°C    | TA ≤ 85°C    | TA ≤ 125°C   |

|---------|--------------|-----------------|--------------|--------------|--------------|

|         | Power Rating | Above TA ≤ 25°C | Power Rating | Power Rating | Power Rating |

| W       | 700 mW       | 5.5 mW/°C       | 452 mW       | 370 mW       | 150 mW       |

# **ELECTRICAL CHARACTERISTICS:**

Unless otherwise stated, these specifications apply for -55°C ≤ TA ≤ 125°C for the UC184X;  $-40^{\circ}$ C  $\leq$  TA  $\leq$  85°C for the UC284X;  $0^{\circ}$ C  $\leq$  TA  $\leq$  70°C for the 384X; Vcc = 15V (Note 5); RT = 10k; CT = 3.3nF, TA=TJ.

| PARAMETER                    | TEST CONDITIONS                                      | UC1842/3/4/5<br>UC2842/3/4/5 |      | UC3842/3/4/5 |      |      | UNITS |       |

|------------------------------|------------------------------------------------------|------------------------------|------|--------------|------|------|-------|-------|

|                              |                                                      | MIN                          | TYP  | MAX          | MIN  | TYP  | MAX   | 1     |

| Reference Section            |                                                      |                              |      |              |      |      |       |       |

| Output Voltage               | $T_J = 25$ °C, $I_O = 1$ mA                          | 4.95                         | 5.00 | 5.05         | 4.90 | 5.00 | 5.10  | V     |

| Line Regulation              | $12 \leq V \text{IN} \leq 25 V$                      |                              | 6    | 20           |      | 6    | 20    | mV    |

| Load Regulation              | $1 \le lo \le 20mA$                                  |                              | 6    | 25           |      | 6    | 25    | mV    |

| Temp. Stability              | (Note 2) (Note 7)                                    |                              | 0.2  | 0.4          |      | 0.2  | 0.4   | mV/°C |

| Total Output Variation       | Line, Load, Temp. (Note 2)                           | 4.9                          |      | 5.1          | 4.82 |      | 5.18  | V     |

| Output Noise Voltage         | $10Hz \le f \le 10kHz$ , $T_J = 25^{\circ}C$ (Note2) |                              | 50   |              |      | 50   |       | μV    |

| Long Term Stability          | Ta = 125°C, 1000Hrs. (Note 2)                        |                              | 5    | 25           |      | 5    | 25    | mV    |

| Output Short Circuit         |                                                      | -30                          | -100 | -180         | -30  | -100 | -180  | mA    |

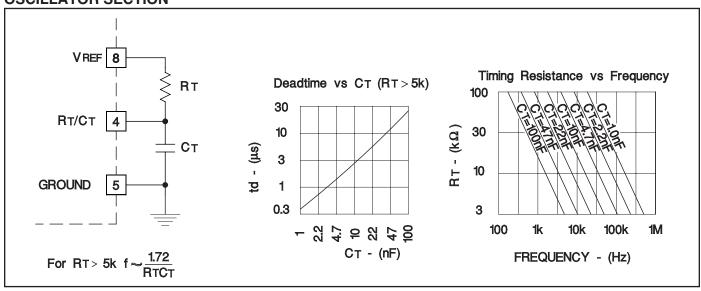

| Oscillator Section           |                                                      |                              |      |              |      |      |       |       |

| Initial Accuracy             | T <sub>J</sub> = 25°C (Note 6)                       | 47                           | 52   | 57           | 47   | 52   | 57    | kHz   |

| Voltage Stability            | 12 ≤ Vcc ≤ 25V                                       |                              | 0.2  | 1            |      | 0.2  | 1     | %     |

| Temp. Stability              | TMIN ≤ TA ≤ TMAX (Note 2)                            |                              | 5    |              |      | 5    |       | %     |

| Amplitude                    | VPIN 4 peak to peak (Note 2)                         |                              | 1.7  |              |      | 1.7  |       | V     |

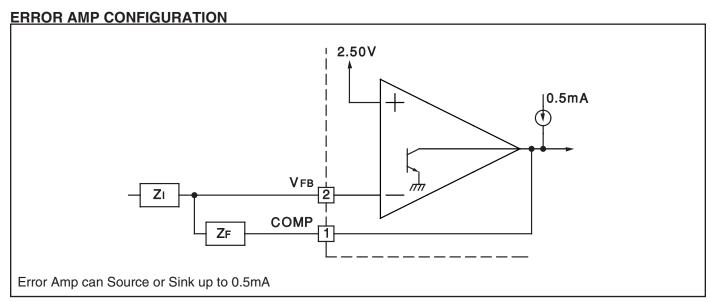

| <b>Error Amp Section</b>     |                                                      |                              |      |              |      |      |       |       |

| Input Voltage                | VPIN 1 = 2.5V                                        | 2.45                         | 2.50 | 2.55         | 2.42 | 2.50 | 2.58  | V     |

| Input Bias Current           |                                                      |                              | -0.3 | -1           |      | -0.3 | -2    | μΑ    |

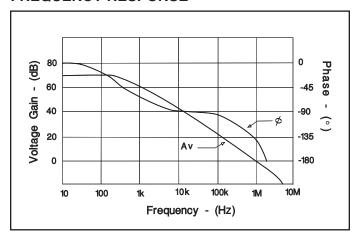

| AVOL                         | $2 \le Vo \le 4V$                                    | 65                           | 90   |              | 65   | 90   |       | dB    |

| Unity Gain Bandwidth         | (Note 2) T <sub>J</sub> = 25°C                       | 0.7                          | 1    |              | 0.7  | 1    |       | MHz   |

| PSRR                         | 12 ≤ Vcc ≤ 25V                                       | 60                           | 70   |              | 60   | 70   |       | dB    |

| Output Sink Current          | VPIN 2 = 2.7V, VPIN 1 = 1.1V                         | 2                            | 6    |              | 2    | 6    |       | mA    |

| Output Source Current        | VPIN 2 = 2.3V, VPIN 1 = 5V                           | -0.5                         | -0.8 |              | -0.5 | -0.8 |       | mA    |

| Vouт High                    | VPIN $2 = 2.3V$ , RL = 15k to ground                 | 5                            | 6    |              | 5    | 6    |       | V     |

| Vout Low                     | VPIN 2 = 2.7V, RL = 15k to Pin 8                     |                              | 0.7  | 1.1          |      | 0.7  | 1.1   | V     |

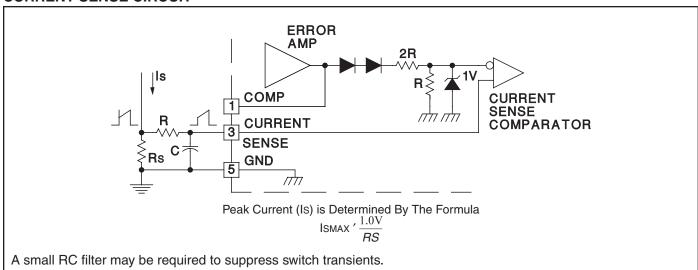

| <b>Current Sense Section</b> |                                                      |                              |      |              |      |      |       |       |

| Gain                         | (Notes 3 and 4)                                      | 2.85                         | 3    | 3.15         | 2.85 | 3    | 3.15  | V/V   |

| Maximum Input Signal         | VPIN 1 = 5V (Note 3)                                 | 0.9                          | 1    | 1.1          | 0.9  | 1    | 1.1   | V     |

| PSRR                         | 12 ≤ V <sub>CC</sub> ≤ 25V (Note 3) (Note 2)         |                              | 70   |              |      | 70   |       | dB    |

| Input Bias Current           |                                                      |                              | -2   | -10          |      | -2   | -10   | μΑ    |

| Delay to Output              | VPIN 3 = 0 to 2V (Note 2)                            |                              | 150  | 300          |      | 150  | 300   | ns    |

Note 2: These parameters, although guaranteed, are not 100% tested in production.

Note 3: Parameter measured at trip point of latch with VPIN 2 = 0.

Note 4:

Gain defined as  $A = \frac{\Delta VPIN \ 1}{\Delta VPIN \ 3}, 0 \le VPIN \ 3 \le 0.8V$

Adjust Vcc above the start threshold before setting at 15V. Note 5:

Output frequency equals oscillator frequency for the UC1842 and UC1843. Note 6: Output frequency is one half oscillator frequency for the UC1844 and UC1845.

Temperature stability, sometimes referred to as average temperature coefficient, is described by the equation:  $Temp Stability = \frac{V_{REF} (max) - VREF (min)}{T_{REF} (max)}$ Note 7:

TJ(max) - TJ(min)

VREF (max) and VREF (min) are the maximum and minimum reference voltages measured over the appropriate temperature range. Note that the extremes in voltage do not necessarily occur at the extremes in temperature.

## **ELECTRICAL CHARACTERISTICS:**

Unless otherwise stated, these specifications apply for  $-55^{\circ}\text{C} \le \text{Ta} \le 125^{\circ}\text{C}$  for the UC184X;  $-40^{\circ}\text{C} \le \text{Ta} \le 85^{\circ}\text{C}$  for the UC284X;  $0^{\circ}\text{C} \le \text{Ta} \le 70^{\circ}\text{C}$  for the 384X; Vcc = 15V (Note 5); RT = 10k; CT = 3.3nF, Ta=TJ.

| PARAMETER                     | TEST CONDITION                                       |     | UC1842/3/4/5<br>UC2842/3/4/5 |     |      | UC3842/3/4/5 |      |    |

|-------------------------------|------------------------------------------------------|-----|------------------------------|-----|------|--------------|------|----|

|                               |                                                      | MIN | TYP                          | MAX | MIN  | TYP          | MAX  | 1  |

| Output Section                |                                                      |     |                              |     |      |              |      |    |

| Output Low Level              | ISINK = 20mA                                         |     | 0.1                          | 0.4 |      | 0.1          | 0.4  | V  |

|                               | ISINK = 200mA                                        |     | 1.5                          | 2.2 |      | 1.5          | 2.2  | V  |

| Output High Level             | ISOURCE = 20mA                                       | 13  | 13.5                         |     | 13   | 13.5         |      | V  |

|                               | ISOURCE = 200mA                                      | 12  | 13.5                         |     | 12   | 13.5         |      | V  |

| Rise Time                     | T <sub>J</sub> = 25°C, C <sub>L</sub> = 1nF (Note 2) |     | 50                           | 150 |      | 50           | 150  | ns |

| Fall Time                     | T <sub>J</sub> = 25°C, C <sub>L</sub> = 1nF (Note 2) |     | 50                           | 150 |      | 50           | 150  | ns |

| Under-voltage Lockout Section | n                                                    | ·   |                              |     |      |              |      |    |

| Start Threshold               | X842/4                                               | 15  | 16                           | 17  | 14.5 | 16           | 17.5 | V  |

|                               | X843/5                                               | 7.8 | 8.4                          | 9.0 | 7.8  | 8.4          | 9.0  | V  |

| Min. Operating Voltage        | X842/4                                               | 9   | 10                           | 11  | 8.5  | 10           | 11.5 | V  |

| After Turn On                 | X843/5                                               | 7.0 | 7.6                          | 8.2 | 7.0  | 7.6          | 8.2  | V  |

| PWM Section                   |                                                      | ·   | •                            |     |      | •            |      |    |

| Maximum Duty Cycle            | X842/3                                               | 95  | 97                           | 100 | 95   | 97           | 100  | %  |

|                               | X844/5                                               | 46  | 48                           | 50  | 47   | 48           | 50   | %  |

| Minimum Duty Cycle            |                                                      |     |                              | 0   |      |              | 0    | %  |

| <b>Total Standby Current</b>  |                                                      |     |                              |     |      |              |      |    |

| Start-Up Current              |                                                      |     | 0.5                          | 1   |      | 0.5          | 1    | mA |

| Operating Supply Current      | VPIN 2 = VPIN 3 = 0V                                 |     | 11                           | 17  |      | 11           | 17   | mA |

| Vcc Zener Voltage             | Icc = 25mA                                           | 30  | 34                           |     | 30   | 34           |      | V  |

Note 2: These parameters, although guaranteed, are not 100% tested in production.

Note 3: Parameter measured at trip point of latch with VPIN 2 = 0

.

Note 4: Gain defined as:  $A = \frac{\Delta VPIN \ 1}{\Delta VPIN \ 3}; 0 \le VPIN \ 3 \le 0.8V$ .

Note 5: Adjust Vcc above the start threshold before setting at 15V.

Note 6: Output frequency equals oscillator frequency for the UC1842 and UC1843.

Output frequency is one half oscillator frequency for the UC1844 and UC1845.

# **UNDER-VOLTAGE LOCKOUT**

During under-voltage lock-out, the output driver is biased to sink minor amounts of current. Pin 6 should be shunted to ground with a bleeder resistor to prevent activating the power switch with extraneous leakage currents.

# **CURRENT SENSE CIRCUIT**

# **OSCILLATOR SECTION**

# **OUTPUT SATURATION CHARACTERISTICS**

# Voc = 15V TA = +25°C TA = -55°C TA = -55°C SOURCE SAT (Voc-Voh) SINK SAT (Vol.) 01 .02 .03 .04 .05 .07 .1 .2 .3 .4 .5 .7 1.0 Output Current, Source or Sink - (A)

# ERROR AMPLIFIER OPEN-LOOP FREQUENCY RESPONSE

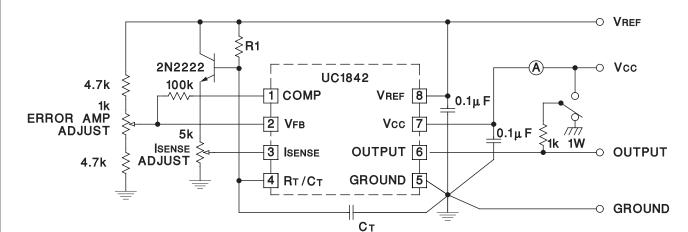

# **OPEN-LOOP LABORATORY FIXTURE**

High peak currents associated with capacitive loads necessitate careful grounding techniques. Timing and bypass capacitors should be connected close to pin 5 in a single point ground. The transistor and 5k potentiometer are used to sample the oscillator waveform and apply an adjustable ramp to pin 3.

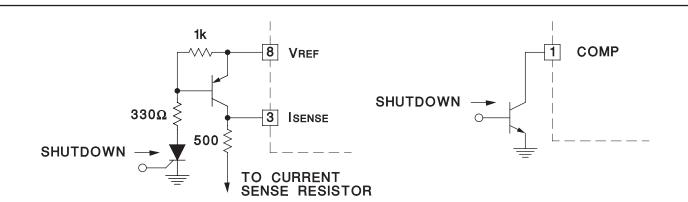

## SHUT DOWN TECHNIQUES

Shutdown of the UC1842 can be accomplished by two methods; either raise pin 3 above 1V or pull pin 1 below a voltage two diode drops above ground. Either method causes the output of the PWM comparator to be high (refer to block diagram). The PWM latch is reset dominant so that the output will remain low until the next

clock cycle after the shutdown condition at pin 1 and/or 3 is removed. In one example, an externally latched shutdown may be accomplished by adding an SCR which will be reset by cycling Vcc below the lower UVLO threshold. At this point the reference turns off, allowing the SCR to reset.

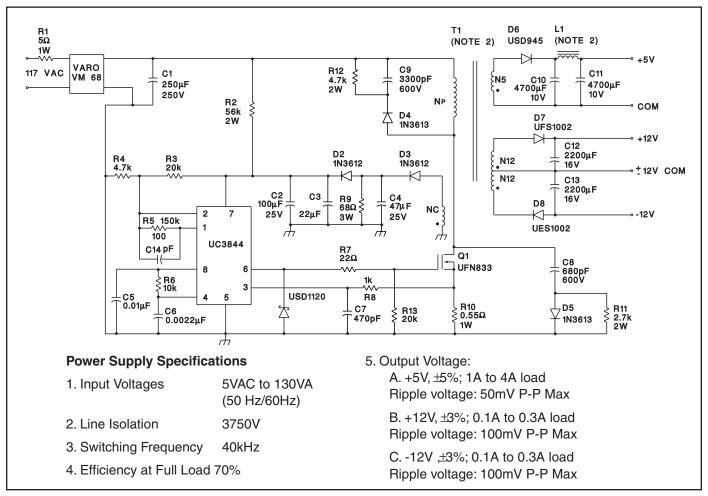

## OFFLINE FLYBACK REGULATOR

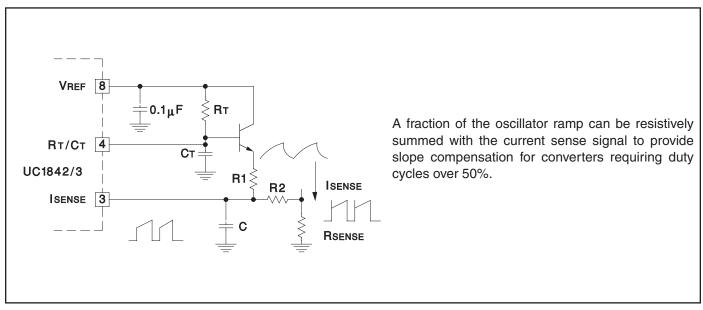

# **SLOPE COMPENSATION**

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.